1Learning Outcomes¶

Translate between S-type assembly instructions and machine instructions.

Reason about why store instructions,

sb,sh, andsw, have their own instruction format.Reason about why the

immimmediate field is split into two bitranges in S-Type format.

🎥 Lecture Video

Our next instruction format is S-Type, the format used for Store instructions sb, sh, and sw. While load instructions fit nicely into the I-Type format, store instructions use registers differently than the instructions we’ve seen so far. We need a special instruction format to translate store instructions into machine code.

Recall from an earlier section:

The store word instruction:

Computes a memory address

R[rs1]+immStore a word from register

rs2,R[rs2][31:0], to this address in memory,M[R[rs1] + imm][31:0].

Stores therefore need the following fields:

rs1: “base” register which stores the base memory addressrs2: “source” register which stores the data to be stored in memoryimm: 2’s complement “offset” to add to the “base” register to form the memory address to use in store (store address = R[base register]) + (immediate offset)opcode(as all instructions do). Stores use opcode0100011.funct3specifies partial stores.

Store instructions have two operand registers, like in R-type instructions, but do not have a destination regsiter rd. Instead, S-type instructions have an immediate value, like in I-type instructions. Therefore, we use a new instruction format: S-type for “Store”-type.

2S-Type: Fields¶

The S-Type instruction format is the fourth row of the Instruction format table of the RISC-V green card.

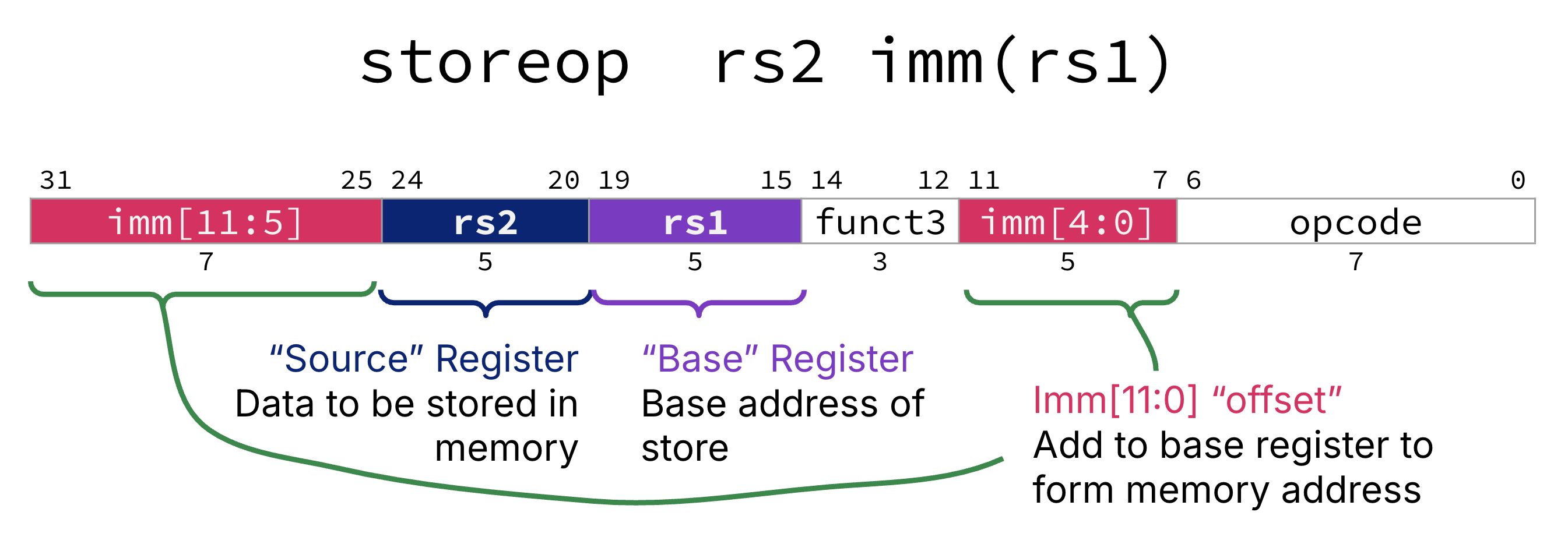

The format for these storeop rs2 imm(rs1) instructions is shown in Figure 1:

Figure 1:The S-Type Instruction Format.

Register operands: Notice that the register fields rs1 and rs2 are in the same positions in S-Type and R-type; this intentional design reduces hardware complexity.

Constant operand: Similar to I-Type, the immediate field imm specifies a 12-bit-wide immediate value. However, in S-type, the immediate field is split into two different bit positions. The lower 5 bits of the immediate imm[4:0] are in bits [11:7] and the upper 7 bits imm[31:25] are in bits [31:25] in the machine code instruction.

The 12-bit immediate is still a two’s complement integer with range to , like in I-type. The difference is that we now have to either split up the bits or put them together to recover the immediate, depending on if we are translating to machine code or to assembly code.

3Assembly Instruction Machine Instruction¶

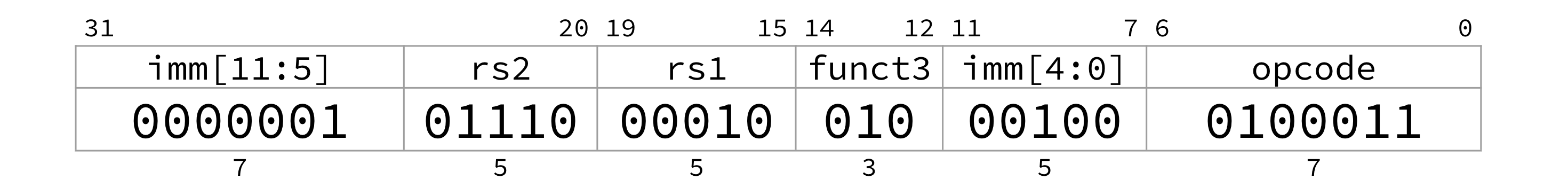

Consider the translation of sw x14 36(x2) to the machine instruction shown in Figure 2.

Figure 2:The S-Type instruction sw x14 36(x2).

We follow the steps for translating assembly into machine code from earlier:

Determine operation field codes.

opcode:0100011for all S-Type instructionsfunct3:010forsw

Translate registers and immediates.

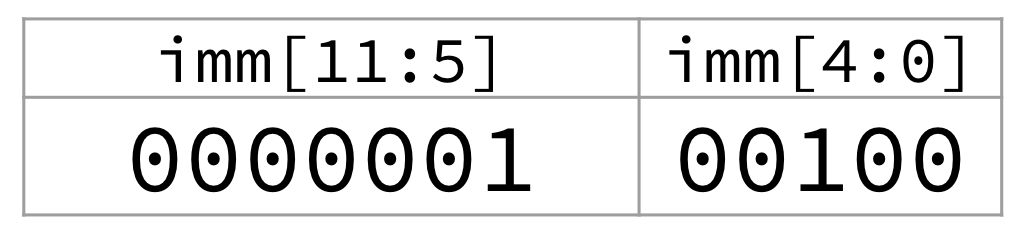

rs1: Registerx2. Translate 2 to 5-bit unsigned integer representation0b00010.rs2: Registerx14. Translate 14 to 5-bit unsigned integer representation0b01110.imm: 36 as a 12-bit two’s complement, split into 7 upper-bits and 5 lower-bits:+36 is

0b0000 0010 0100.Split offset bits into upper and lower bit positions as shown in Figure 3: upper-bits

imm[11:5] = 0b0000001, lower-bitsimm[4:0] = 0b00100

(if needed) Convert to hexadecimal.

We leave this as an exercise to you!

Figure 3:Immediate (offset) value for the S-Type instruction sw x14 36(x2).

4S-Type vs. I-Type vs. R-Type¶

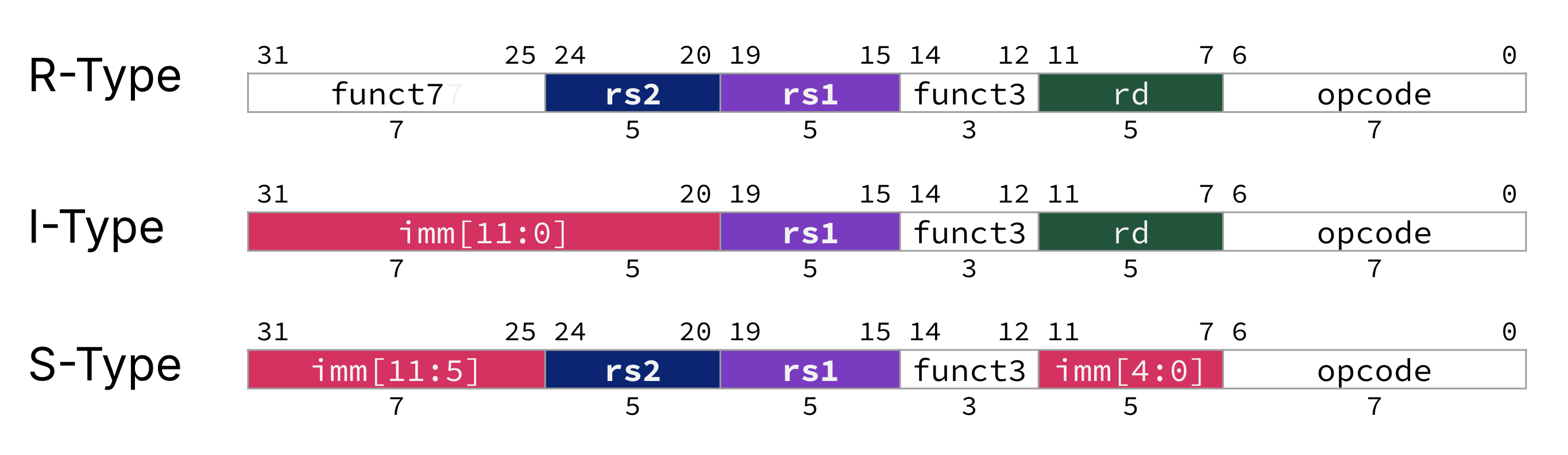

Figure 4 compares the three instruction formats we have seen so far:

Figure 4:S-Type instruction set comparison to I-type and R-Type instruction sets.

Again, like in I-Type, S-Type instructions expand the imm field across the R-Type’s funct7 field. However, in contrast to I-Type, store instructions use a second source operand register rs2 and need to use bits [24:20] to encode which register to use to access the data to be stored to memory.

However, if we only had the 7-bit field replacing funct7, then we’d only be able to represent 128 immediate values. Since S-Type instructions do not write to a destination register rd, we have another 5-bit field to use to represent a 12-bit imm field. The immediate in store instructions represents an offset to be added to a base address. These offset constants are frequently short and can fit into the 12-bit imm field.

The consistency between the three instruction type formats allows for simple hardware design!

5Reference for S-Type Instructions¶

This section is intended as a reference for S-Type instructions based on what you learned in this section.

Consider the S-Type instructions shown in Table 1 from the RISC-V green card.

Table 1:RV32I Instructions: S-Type

| Instruction | imm[11:15] | rs2 | rs1 | funct3 | imm[4:0] | opcode |

|---|---|---|---|---|---|---|

sb | imm[11:5] | rs2 | rs1 | 000 | imm[4:0] | 0100011 |

sh | imm[11:5] | rs2 | rs1 | 001 | imm[4:0] | 0100011 |

sw | imm[11:5] | rs2 | rs1 | 010 | imm[4:0] | 0100011 |

Recall that store instructions write to memory with only specified bytes. We do not need sign/logical extension.